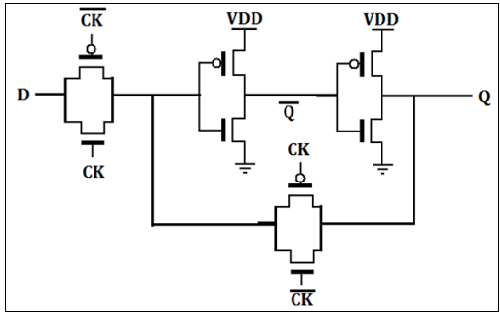

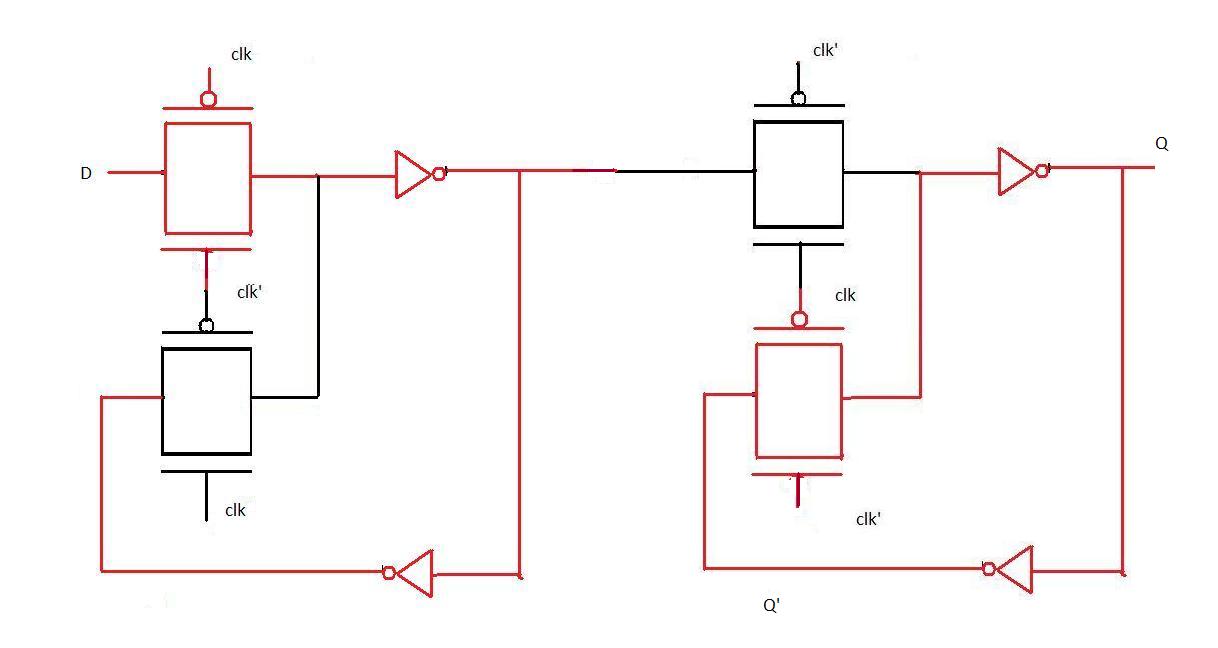

Various flip-flops a Transmission-gate-based master-slave flip-flop... | Download Scientific Diagram

Figure 1 from A NOVEL DESIGN OF COUNTER USING TSPC D FLIP-FLOP FOR HIGH PERFORMANCE AND LOW POWER VLSI DESIGN APPLICATIONS USING 45 NM CMOS TECHNOLOGY Ms . | Semantic Scholar

![Implement D flip-flop using Static CMOS. What are other design methods for it? [10] OR Draw D flipflop using CMOS and explain the working. Implement D flip-flop using Static CMOS. What are other design methods for it? [10] OR Draw D flipflop using CMOS and explain the working.](https://i.imgur.com/ksiy7VH.png)

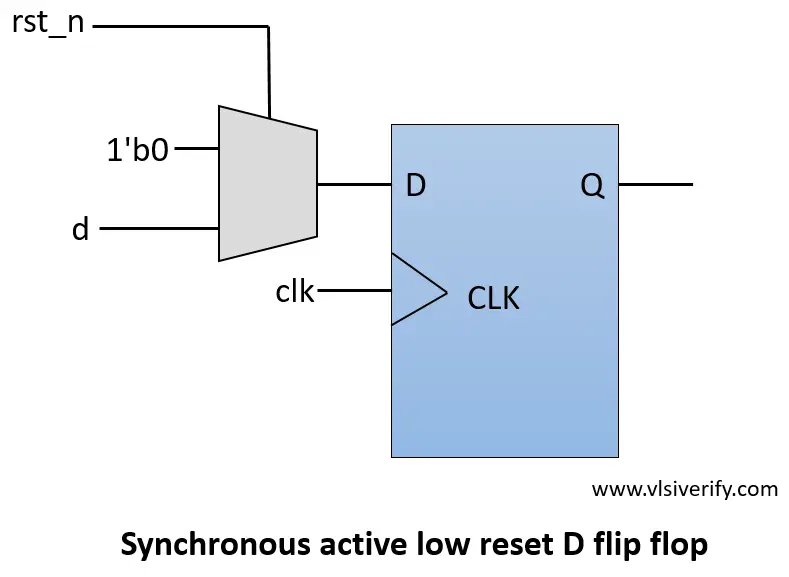

![18b] D Flip Flop - master slave DFF - DFF with reset - YouTube 18b] D Flip Flop - master slave DFF - DFF with reset - YouTube](https://i.ytimg.com/vi/LE8pIP6klb0/maxresdefault.jpg)